新書推薦:

《

人类简史系列(白金纪念版)(套装共4册)

》

售價:NT$

1612.0

《

深度学习推荐系统2.0

》

售價:NT$

653.0

《

小欢喜2:南京爱情故事

》

售價:NT$

352.0

《

分解工作法:聪明人如何解决复杂问题

》

售價:NT$

305.0

《

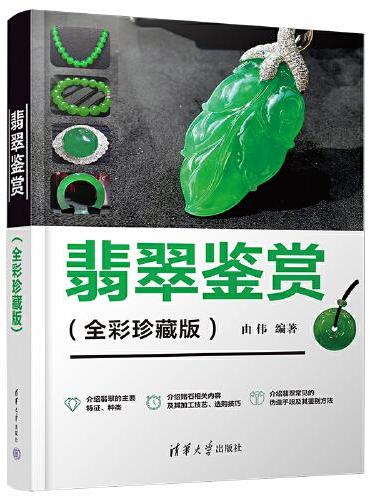

翡翠鉴赏(全彩珍藏版)

》

售價:NT$

352.0

《

艺文志·石川啄木:日本的第一个现代人

》

售價:NT$

347.0

《

DK葡萄酒大百科:一本关于葡萄酒的百科全书

》

售價:NT$

2540.0

《

未来简史 从智人到智神(2025白金纪念版)

》

售價:NT$

403.0

|

| 內容簡介: |

|

本书聚焦人工智能处理器硬件设计的算力瓶颈问题,介绍了神经网络处理内核电路与系统的设计目标、优化技术、评价方式,以及应用领域。全书共9章,以人工智能硬件芯片组织架构的核心处理单位“卷积神经网络”在系统架构层面的算力性能提升为目标,在回顾了CPU、GPU和NPU等深度学习硬件处理器的基础上,重点介绍主流的人工智能处理器的各种架构优化技术,包括并行计算、流图理论、加速器设计、混合内存与存内计算、稀疏网络管理,以及三维封装处理技术,以业界公认的测试集与方法为依据,展现不同架构设计的处理器在功耗、性能及成本指标等方面不同程度的提升,深入探讨优化整体硬件的各种方法。

|

| 關於作者: |

|

Albert Chun Chen Liu(刘峻诚) 加州大学洛杉矶分校电子工程博士,本科毕业于台湾成功大学,耐能(Kneron)人工智能公司创始人兼首席执行官。他曾在高通公司、三星电子研发中心、晨星半导体(MStar)和无线信息公司(Wireless Info)担任研发和管理职务,于2015年在美国圣迭戈创办耐能人工智能公司,并受邀在美国加州大学讲授计算机视觉技术和人工智能课程,同时担任多个国际知名学术期刊的技术审稿人。他在人工智能、计算机视觉和视频处理领域拥有30 多项国际专利,先后在国际重要期刊发表70 多篇论文,并获得了2021年IEEE 达林顿奖(Darlington Award),2022年潘文渊文教基金会物联网创新应用奖,2023年IEEE CTSoc颁发的企业创新领袖奖。王立宁,2000年毕业于北京邮电大学,获工学博士学位。长期在海外从事集成电路相关设计工作,曾经在英特尔研发中心从事FPGA的技术开发。曾经出版十多本相关技术图书或译著,在二十多年的实践中,获得三十多项国家发明专利授权。

|

| 目錄:

|

目 录

第1章 人工智能技术简介1

1.1 发展简史2

1.2 神经网络模型3

1.3 神经网络分类4

1.3.1 监督学习4

1.3.2 半监督学习5

1.3.3 无监督学习5

1.4 神经网络框架5

1.5 神经网络的比较7

思考题9

原著参考文献9

第2章 深度学习加速器的设计11

2.1 神经网络的网络层13

2.1.1 卷积层13

2.1.2 激活层14

2.1.3 池化层15

2.1.4 批量归一化层16

2.1.5 丢弃层17

2.1.6 全连接层17

2.2 设计深度学习加速器所面临的挑战18

思考题19

原著参考文献20

第3章 人工智能硬件加速器的并行结构21

3.1 英特尔中央处理器(CPU)21

3.1.1 天湖网状架构22

3.1.2 英特尔超路径互连(UPI)24

3.1.3 子非统一内存访问集群(SNC)25

3.1.4 缓存架构的调整26

3.1.5 单/多插槽并行处理27

3.1.6 高级矢量软件扩展27

3.1.7 深度神经网络的数学内核库(MKL-DNN)29

3.2 英伟达图形处理器(GPU)33

3.2.1 张量计算核心架构36

3.2.2 维诺格拉德变换38

3.2.3 同步多线程(SMT)40

3.2.4 第二代高带宽内存(HBM2)40

3.2.5 NVLink2配置41

3.3 英伟达深度学习加速器(NVDLA)43

3.3.1 卷积运算43

3.3.2 单点数据运算44

3.3.3 平面数据运算44

3.3.4 多平面运算44

3.3.5 数据存储和重塑操作44

3.3.6 系统配置45

3.3.7 外部接口45

3.3.8 软件设计46

3.4 谷歌张量处理器(TPU)46

3.4.1 系统架构47

3.4.2 乘法-累加(MAC)脉冲阵列49

3.4.3 新的大脑浮点格式50

3.4.4 性能比较51

3.4.5 云TPU配置51

3.4.6 云软件架构53

3.5 微软弹射器结构加速器(NPU)54

3.5.1 系统配置57

3.5.2 弹射器架构57

3.5.3 矩阵-向量乘法器58

3.5.4 分层解码与调度(硬盘)60

3.5.5 稀疏矩阵-向量乘法61

思考题63

原著参考文献64

第4章 基于流图理论的加速器设计66

4.1 Blaize流图处理器66

4.1.1 流图模型66

4.1.2 深度优先调度方法68

4.1.3 流图处理器架构69

4.2 Graphcore智能处理器72

4.2.1 智能处理器(IPU)架构72

4.2.2 累加矩阵积(AMP)单元72

4.2.3 内存架构74

4.2.4 互连架构74

4.2.5 批量同步并行模型75

思考题76

原著参考文献76

第5章 加速器的卷积计算优化78

5.1 深度学习加速器—以DCNN加速器为例78

5.1.1 系统架构78

5.1.2 滤波器分解80

5.1.3 流处理架构83

5.1.4 池化85

5.1.5 卷积单元(CU)引擎86

5.1.6 累加(ACCU)缓冲区87

5.1.7 模型压缩87

5.1.8 系统性能88

5.2 Eyeriss加速器89

5.2.1 Eyeriss系统架构89

5.2.2 二维卷积运算到一维乘法运算的转换90

5.2.3 数据流固定(SD)92

5.2.4 行固定(RS)数据流95

5.2.5 游程长度压缩(RLC)算法98

5.2.6 全局缓冲区(GLB)99

5.2.7 Eyeriss PE架构99

5.2.8 片上网络(NoC)100

5.2.9 Eyeriss v2系统架构104

5.2.10 分层网状网106

5.2.11 压缩稀疏列格式111

5.2.12 行固定加(RS+)数据流112

5.2.13 系统性能112

思考题114

原著参考文献114

第6章 存内计算116

6.1 Neurocube加速器116

6.1.1 混合内存立方体(HMC)116

6.1.2 以内存为中心的神经计算118

6.1.3 可编程神经序列发生器119

6.1.4 系统性能121

6.2 Tetris加速器121

6.2.1 内存层次结构121

6.2.2 存内累加122

6.2.3 数据调度123

6.2.4 神经网络的vault分区124

6.2.5 系统性能125

6.3 NeuroStream加速器126

6.3.1 系统架构126

6.3.2 NeuroStream协处理器127

6.3.3 四维分块的机制128

6.3.4 系统性能130

思考题131

原著参考文献131

第7章 近内存体系架构132

7.1 DaDianNao超级计算机132

7.1.1 内存配置132

7.1.2 神经功能单元133

7.1.3 系统性能135

7.2 Cnvlutin加速器137

7.2.1 基本卷积运算137

7.2.2 系统架构139

7.2.3 处理顺序140

7.2.4 无零神经元阵列格式(ZFNAf)143

7.2.5 调度器143

7.2.6 动态修剪144

7.2.7 系统性能144

7.2.8 原生或编码(RoE)格式145

7.2.9 矢量无效激活标识符(VIAI)格式145

7.2.10 跳过无效激活146

7.2.11 跳过无效权重146

思考题148

原著参考文献148

第8章 加速器的网络稀疏性149

8.1 能效推理引擎(EIE)加速器149

8.1.1 前导非零检测(LNZD)网络149

8.1.2 中央控制单元(CCU)150

8.1.3 处理元件(PE)150

8.1.4 深度压缩150

8.1.5 稀疏矩阵计算153

8.1.6 系统性能154

8.2 寒武纪X加速器154

8.2.1 计算单元156

8.2.2 缓冲区控制器157

8.2.3 系统性能159

8.3 稀疏卷积神经网络(SCNN)加速器160

8.3.1 SCNN加速器的PT-IS-CP-密集数据流160

8.3.2 SCNN加速器的PT-IS-CP-稀疏数据流162

8.3.3 SCNN加速器的分块架构162

8.3.4 SCNN加速器的PE架构163

8.3.5 SCNN加速器的数据压缩164

8.3.6 SCNN加速器的系统性能164

8.4 SeerNet加速器166

8.4.1 低位量化167

8.4.2 有效量化167

8.4.3 量化卷积168

8.4.4 推理加速器170

8.4.5 稀疏性掩码编码170

8.4.6 系统性能170

思考题171

原著参考文献171

第9章 加速器芯片的三维堆叠工艺173

9.1 三维集成电路架构173

9.2 配电网络174

9.3 三维网桥工艺176

9.3.1 三维片上网络177

9.3.2 多通道高速链路178

9.4 低功耗技术178

9.4.1 电源选通178

9.4.2 时钟选通180

思考题180

原著参考文献181

附录A 神经网络拓扑182

附录B 中英文词汇表183

|

|